캐시 메모리

From CS Wiki

- Cache Memory

CPU와 주기억장치 사이에 있는 고속 메모리로, CPU와 주기억장치의 처리 속도 차이를 보완하기 위한 기억장치

구현 원리[edit | edit source]

- 구역성(Locality)의 원리에 따라 CPU가 참조하는 데이터를 예측하여 캐시 메모리에 미리 담아 둔다.

- 캐시 메모리에 있는 데이터는 주기억장치를 참조하지 않고 고속의 캐시메모리에서 바로 가져와 실행한다.

캐시 메모리 성능[edit | edit source]

- Hit Rate(적중률) = 적중 횟수 / 접근 횟수 * 100

- Miss Rate(실패율) = (100 - 적중률)

메모리 사상 기법[edit | edit source]

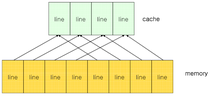

직접 사상[edit | edit source]

- Direct Mapping

- 메모리 주소와 캐시의 순서를 일치시킴

- ex) 메모리가 1~100, 캐시가 1~10으로 가정하면

- 1~10까지의 메모리는 캐시의 1에 할당, 11~20까지의 메모리는 캐시의 2에 할당

- 구현 정말 간단하지만 캐싱 효율이 떨어져 잦은 교체 발생

- 적중률이 낮고 성능이 낮은 단순한 방식

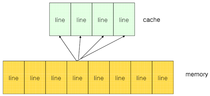

연관 사상[edit | edit source]

- Fully Associative

- 순서를 일치시키지 않음

- 필요한 메모리값을 캐시의 어디든 저장 가능

- 찾는 과정은 느리지만 필요한 캐시들 위주로 저장할 수 있기 때문에 적중률이 높음

- 캐시가 일반 메모리보다 속도가 훨씬 빠르므로 적중률이 높은 것이 유리

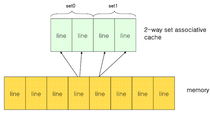

직접/연관 사상[edit | edit source]

- Set Associative

- 연관매핑에 직접매핑을 합쳐 놓은 방식

- 순서를 일치시키고 저장하되, 일정 그룹을 두어 그 그룹 내에서 저장토록 함

- ex) 메모리가 1~100, 캐시가 1~10으로 가정하면

- 캐시 1~5에는 1~50의 데이터 저장 가능

- 블록화가 되어 있으므로 검색 효율 증가, 적중률도 일정 수준 보장

교체 알고리즘[edit | edit source]

- Data Replacement Algorithm

※ 직접 사상의 경우 교체 알고리즘 선택 불가

- Random

- 무작위로 선택하여 교체

- 비효율적이지만 구현이 간단하여 많이 사용

- Round Robin

- 공평하게 돌아가면서 선택

- 구현이 간단하지만 효율이 좋지 않음

- LRU(Least Recently Used)

- 가장 오랫동안 이용되지 않은 데이터 교체

- 가장 이상적이지만 CPU Cache에서는 판단이 어려움

쓰기 정책[edit | edit source]

- Write Strategy

- Write Through

- 데이터 변경 시 캐시와 메모리에 곧바로 기록

- 구현이 쉬우며 일관성 문제가 발생하지 않음

- 잦은 쓰기로 속도 느려짐

- Write Back

- 캐시에 먼저 기록하고 메모리엔 나중에 기록

- 속도가 빠르지만 일관성 문제 발생 가능성

- Dirty Bit, Flag 등 이용 필요

설계 시 고려사항[edit | edit source]

- 캐시 메모리 사이즈

- 전송 블록 사이즈

- 교체 알고리즘